실리콘 웨이퍼 기판 위에 실리콘 원자층을 하나 더 성장시키는 것은 여러 가지 장점이 있습니다.

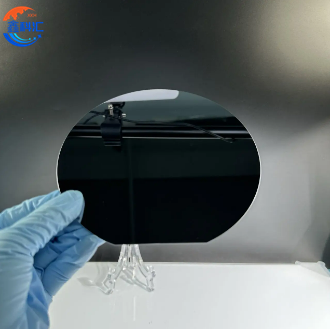

CMOS 실리콘 공정에서 웨이퍼 기판 상의 에피택셜 성장(EPI)은 매우 중요한 공정 단계입니다.

1. 결정 품질 향상

초기 기판 결함 및 불순물: 제조 공정 중 웨이퍼 기판에 특정 결함 및 불순물이 존재할 수 있습니다. 에피택셜 층 성장을 통해 기판 상에 결함 및 불순물 농도가 낮은 고품질 단결정 실리콘 층을 생성할 수 있으며, 이는 후속 소자 제작에 매우 중요합니다.

균일한 결정 구조: 에피택셜 성장은 더욱 균일한 결정 구조를 보장하여 기판 재료의 결정립 경계 및 결함의 영향을 줄이고 웨이퍼의 전반적인 결정 품질을 향상시킵니다.

2. 전기적 성능을 향상시킵니다.

소자 특성 최적화: 기판 위에 에피택셜 층을 성장시킴으로써 실리콘의 도핑 농도와 종류를 정밀하게 제어하여 소자의 전기적 성능을 최적화할 수 있습니다. 예를 들어, 에피택셜 층의 도핑 농도를 미세하게 조절하여 MOSFET의 문턱 전압 및 기타 전기적 매개변수를 제어할 수 있습니다.

누설 전류 감소: 고품질 에피택셜 층은 결함 밀도가 낮아 소자의 누설 전류를 줄이는 데 도움이 되며, 결과적으로 소자의 성능과 신뢰성을 향상시킵니다.

3. 전기적 성능을 향상시킵니다.

소자 크기 축소: 7nm, 5nm와 같은 초소형 공정 노드에서는 소자의 소자 크기가 지속적으로 작아짐에 따라 더욱 정교하고 고품질의 소재가 요구됩니다. 에피택셜 성장 기술은 이러한 요구를 충족하여 고성능 및 고밀도 집적 회로 제조를 지원합니다.

항복 전압 향상: 에피택셜 층은 더 높은 항복 전압을 갖도록 설계할 수 있으며, 이는 고출력 및 고전압 소자 제조에 매우 중요합니다. 예를 들어, 전력 소자에서 에피택셜 층은 소자의 항복 전압을 향상시켜 안전 작동 범위를 넓힐 수 있습니다.

4. 공정 호환성 및 다층 구조

다층 구조: 에피택셜 성장 기술은 기판 위에 다양한 도핑 농도와 종류를 가진 여러 층으로 구성된 구조를 성장시킬 수 있게 해줍니다. 이는 복잡한 CMOS 소자를 제조하고 3차원 집적화를 구현하는 데 매우 유리합니다.

호환성: 에피택셜 성장 공정은 기존 CMOS 제조 공정과 호환성이 매우 높아 공정 라인을 크게 수정할 필요 없이 현재 제조 워크플로우에 쉽게 통합할 수 있습니다.

요약: CMOS 실리콘 공정에서 에피택셜 성장 기술의 주요 목적은 웨이퍼 결정 품질 향상, 소자 전기적 성능 최적화, 첨단 공정 노드 지원, 그리고 고성능 및 고밀도 집적 회로 제조 요구 충족입니다. 에피택셜 성장 기술은 재료의 도핑 및 구조를 정밀하게 제어할 수 있게 하여 소자의 전반적인 성능과 신뢰성을 향상시킵니다.

게시 시간: 2024년 10월 16일