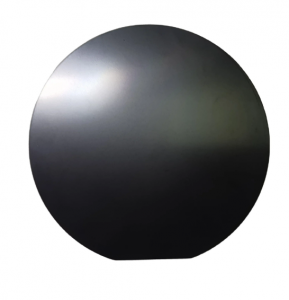

8인치 및 6인치 SOI(실리콘 온 인슐레이터) 웨이퍼 상의 SOI 웨이퍼 절연체

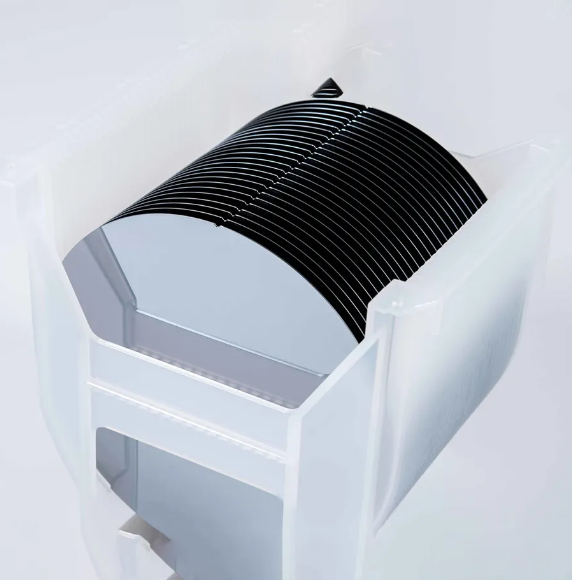

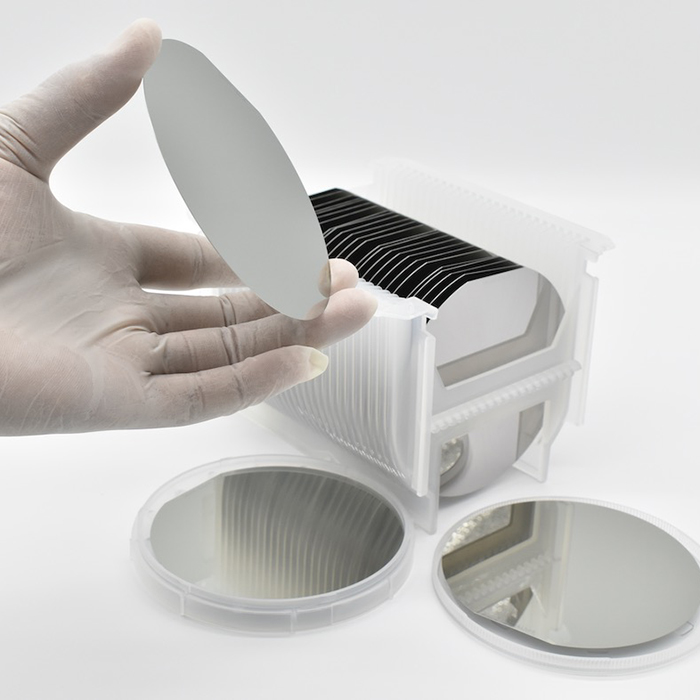

웨이퍼 박스 소개

상부 실리콘 층, 절연 산화막 층, 그리고 하부 실리콘 기판으로 구성된 3층 SOI 웨이퍼는 마이크로일렉트로닉스 및 RF 분야에서 탁월한 장점을 제공합니다. 고품질 결정질 실리콘으로 이루어진 상부 실리콘 층은 복잡한 전자 부품을 정밀하고 효율적으로 집적할 수 있도록 합니다. 기생 정전 용량을 최소화하도록 세심하게 설계된 절연 산화막 층은 불필요한 전기적 간섭을 완화하여 소자 성능을 향상시킵니다. 하부 실리콘 기판은 기계적 지지력을 제공하고 기존 실리콘 가공 기술과의 호환성을 보장합니다.

마이크로일렉트로닉스 분야에서 SOI 웨이퍼는 뛰어난 속도, 전력 효율성 및 신뢰성을 갖춘 첨단 집적 회로(IC) 제작의 기반이 됩니다. 3층 구조 덕분에 CMOS(상보형 금속 산화물 반도체) IC, MEMS(미세 전기 기계 시스템) 및 전력 소자와 같은 복잡한 반도체 장치를 개발할 수 있습니다.

RF 영역에서 SOI 웨이퍼는 RF 장치 및 시스템 설계 및 구현에 있어 탁월한 성능을 보여줍니다. 낮은 기생 정전 용량, 높은 항복 전압, 그리고 우수한 절연 특성 덕분에 RF 스위치, 증폭기, 필터 및 기타 RF 부품에 이상적인 기판으로 사용됩니다. 또한, SOI 웨이퍼의 고유한 방사선 내성은 극한 환경에서의 신뢰성이 매우 중요한 항공우주 및 방위 산업 분야에 적합합니다.

더 나아가 SOI 웨이퍼의 다재다능함은 광자 집적 회로(PIC)와 같은 신흥 기술로까지 확장되며, 단일 기판에 광학 및 전자 부품을 통합하는 것은 차세대 통신 및 데이터 통신 시스템에 큰 가능성을 제시합니다.

요약하자면, 3층 구조의 실리콘 온 인슐레이터(SOI) 웨이퍼는 마이크로일렉트로닉스 및 RF 응용 분야 혁신의 최전선에 서 있습니다. 독특한 구조와 탁월한 성능 특성은 다양한 산업 분야의 발전을 이끌고 기술의 미래를 형성합니다.

상세도